## PERANCANGAN RANGKAIAN PENCACAH RADIASI $\alpha$ DAN $\beta$ DENGAN PENEKANAN LATAR BELAKANG, YANG DIPASANGKAN PADA SLOT IBM-PC

Didi Gayani, Lely Y, M Saleh, Sugiri

Pusat Penelitian Teknik Nuklir - Badan Tenaga Atom Nasional

### ASTRAK

PERANCANGAN RANGKAIAN PENCACAH RADIASI  $\alpha$  DAN  $\beta$  DENGAN PENEKANAN LATAR BELAKANG, YANG DIPASANGKAN PADA SLOT IBM-PC. Dirancang sistem pencacah radiasi  $\alpha$  dan  $\beta$  dengan penekanan sinyal latar belakang, dalam bentuk kartu antarmuka, yang dipasang pada slot IBM PC. Sistem yang dibuat mengaitkan penggunaan rangkaian anti koinsiden dengan pencacah 3 kanal untuk  $\alpha$ ,  $\beta$  dan  $\gamma$  yang dipasang pada slot IBM PC, dan dioperasikan melalui perangkat lunak. Pengujian sistem ini dilakukan dengan mengoperasikan rangkaian yang dibuat pada sebuah peralatan Pencacah Latar Rendah Canberra, dengan maksud untuk mengambil sinyal mentah dari detektor sampel dan detektor guard setelah amplifikasi yang terpasang pada peralatan tersebut. Rangkaian anti koinsiden berfungsi menekan sinyal latar yang berasal dari sinar  $\gamma$  atau sinar kosmis, kemudian selain itu rangkaian ini berfungsi membedakan radiasi  $\alpha$  dan  $\beta$  berdasarkan pada amplituda pulsa yang datang dari detektor, dan memisahkannya dalam kanal yang bersangkutan. Rangkaian pencacah berfungsi sebagai pencacah sinyal yang datang pada kanal kanal bersangkutan, dalam perioda yang ditentukan.

### ABSTRACT

DESIGN OF CIRCUIT FOR  $\alpha$  AND  $\beta$  RADIATION COUNTING SYSTEM WITH BACK-GROUND SUPPRESSION INSTALLED ON THE SLOT OF IBM PC. The counting system for  $\alpha/\beta$  radiation with background suppression has been designed in the form of interface card for installed on the IBM PC. The system consist of anticoincidence circuit and three counters for  $\alpha$ ,  $\beta$ ,  $\gamma$  those are controlled by software on the IBM PC. The evaluation of the system is performed by attaching the circuit on the  $\alpha/\beta$  system of Canberra model 2400 in order to get raw signals from sample and guard detector after amplification. The circuit of anticoincidence is used to suppress the background coming from  $\gamma$  ray or cosmic ray and also to distinguish  $\alpha$  radiation from  $\beta$  radiation refers, to their amplitude coming from the sample detector. The counters act to count the signals coming from related channels in the period of time being determined.

### PENDAHULUAN

Untuk mencacah bahan yang memancarkan radiasi  $\alpha$  atau  $\beta$  yang mempunyai intensitas rendah diperlukan interval waktu pencacahan yang cukup lama dan fasilitas penekanan sinyal latar, agar dapat diperoleh informasi pengukuran yang optimal. Dalam mengukur radiasi  $\alpha$  atau  $\beta$  dengan intensitas rendah latar yang berasal dari radiasi  $\gamma$ , dan radiasi kosmik perlu diredam. Untuk meredam sinyal latar dapat digunakan pelindung timah hitam di sekeliling detektor sehingga radiasi latar yang berasal dari sinar kosmis tertahan oleh pelindung timah hitam sebelum mencapai detektor. Sedangkan radiasi  $\gamma$  yang menyertai bahan yang diukur harus bisa diredam dengan menggunakan anti *coincidence gating*, yang pada dasarnya menggunakan 2 buah detektor proporsional yang disebut detektor sampel, dan detektor guard.

Kedua detektor tersebut sangat peka pada adanya ion yang dihasilkan oleh partikel bermuatan, dan dapat mendeteksi hampir semua partikel yang melewatinya. Detektor sampel mempunyai lapisan jendela yang sangat tipis, yang memisahkan kamar pendeksi dan bahan yang diukur. Detektor guard dibuat dengan lapisan aluminium setebal 1,6 mm pada semua sisinya. Partikel  $\alpha$  dan  $\beta$  dapat dengan bebas melewati detektor sampel, dan dideteksi, tetapi ditahan sebelum mencapai detektor guard oleh dinding aluminium setebal 3,2 mm di sisi belakang detektor sampel. Hanya energi  $\gamma$  yang tinggi dan sinar kosmis yang dapat mencapai detektor guard. Kedua radiasi tersebut, yang disebut radiasi latar karena dapat mencapai kedua detektor proporsional. Dengan teknik anti *coincidence gating* sinyal dari kedua detektor

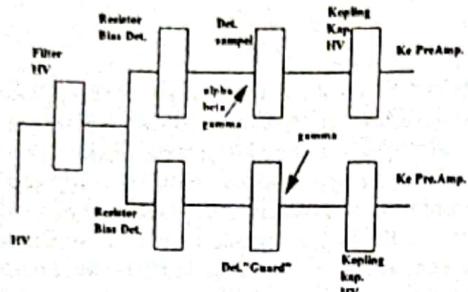

harus saling menghilangkan dan tidak tercah. Gambar 1 memperlihatkan diagram fungsi dari sistem unit pendekatan, dan Gambar 2 memperlihatkan diagram blok pengukuran dari sistem peralatan pencacah radiasi  $\alpha$  dan  $\beta$  dengan penekanan latar belakang.

#### Pemisahan radiasi $\alpha$ dan $\beta$

Detektor proporsional sangat peka pada

Gambar 1. Diagram fungsi dari unit pendekatan

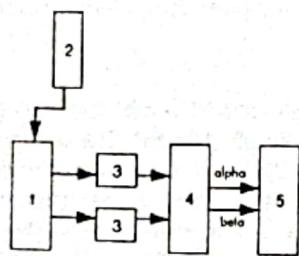

Gambar 2. Diagram blok pencacah  $\alpha$  dan  $\beta$  dengan penekanan latar

#### Keterangan:

1. Unit Detektor proporsional : Detektor sinyal/ sampel dan guard

2. Unit Tegangan tinggi

3. Unit Penguat awal dan Penguat pulsa

4. Unit Rangkaian Antikoinsidens dan gerbang keluaran

5. Unit Pencacah

adanya ion yang dihasilkan oleh partikel bermuatan, dan dapat mendekati hampir semua partikel yang melintasi detektor. Detektor sampel dikonstruksi sedemikian rupa sehingga kamar pendekatan hanya dipisahkan oleh jendela yang sangat tipis dari sampelnya. Pada detektor guard dinding setebal 1,6 mm mengelilingi semua sisinya. Partikel  $\alpha$  dan  $\beta$  dari suatu sampel dapat dengan bebas melewati jendela detektor sampel dan dideteksi, tetapi ditahan sebelum partikel tersebut mencapai detektor guard oleh lempeng tembaga setebal 3,2 mm di sisi

belakang detektor sampel. Hanya  $\gamma$  dengan energi tinggi dan radiasi kosmik yang dapat mencapai detektor guard. Kedua tipe radiasi yang berasal dari luar disebut radiasi latar. Tanpa pengaruh dari radiasi latar, hanya radiasi  $\alpha$  dan  $\beta$  yang berasal dari sampel tercatat dalam pencacahan. Sifat dari detektor sampel memungkinkan pemisahan  $\alpha$  dari  $\beta$  karena rapat ionisasi tiap partikel berbeda. Karena  $\alpha$  mengionisasi gas lebih banyak dari pada yang dihasilkan oleh  $\beta$ , charge sensitive preamplifier menghasilkan pulsa listrik yang lebih tinggi untuk partikel  $\alpha$  dibandingkan dengan partikel  $\beta$ . Jadi untuk penentuan sinyal yang berasal dari partikel  $\alpha$  dan yang berasal dari partikel  $\beta$  dilakukan pemisahan berdasarkan diskriminasi tinggi pulsa. Besarnya tegangan diskriminasi sebagai pembeda radiasi yang berasal dari kedua partikel tersebut didapat dengan percobaan. Besarnya tegangan kerja detektor juga mempengaruhi tinggi pulsa yang dihasilkan. Tegangan kerja detektor untuk mengukur radiasi  $\alpha$  biasanya lebih rendah dari pada tegangan kerja detektor untuk mengukur radiasi  $\beta$ . Dalam pengukuran simultan untuk radiasi  $\alpha$  dan  $\beta$ , biasanya dipasang tegangan kerja tertentu agar sinyal dari radiasi  $\alpha$  maupun  $\beta$  dapat dideteksi. Besarnya pulsa keluaran penguat yang disebabkan oleh partikel  $\alpha$  berkisar 40 kali lebih besar dari pulsa yang disebabkan oleh partikel  $\beta$ . Jika partikel  $\alpha$  menghasilkan pulsa setinggi 10 volt, partikel  $\beta$  menghasilkan pulsa setinggi 0,25 volt, dan kita dapat memilih angka diantara nilai tersebut sebagai batas pemisah radiasi  $\alpha$  dan  $\beta$ . Penentuan nilai batas pemisah tersebut harus ditentukan secara teliti melalui percobaan.

## BAHAN DAN TATA KERJA

Secara keseluruhan sistem terdiri dari :

1. Detektor proporsional sebanyak 2 buah yang dikonstruksi secara khusus, dan disebut detektor sampel dan detektor guard.

2. Sebuah pencatu tegangan tinggi untuk memberi catu daya operasi kedua detektor proporsional. Pengaturan tegangan tinggi untuk operasi kerja detektor ini, tergantung pada model pengukuran yang diinginkan. Hal ini karena pengukuran radiasi  $\alpha$  atau  $\beta$ , memerlukan tegangan tinggi optimal yang berbeda. Sebagai contoh dalam peralatan ini telah disarankan bahwa untuk pengukuran radiasi  $\alpha$  digunakan tegangan tinggi 1000 Volt, sedangkan untuk pengukuran

- radiasi beta atau pengukuran simultan digunakan tegangan 1440 Volt.

3. Penguat awal dan penguat akhir yang identik untuk masing-masing sinyal keluaran detektor.

4. Beberapa kanal pencacahan untuk kanal pencacahan intensitas radiasi.

5. Rangkaian anti koinsiden untuk menekan sinyal latar belakang.

6. Unit monitor penayang untuk menampilkan hasil pengukuran.

7. Perangkat lunak sebagai instruksi urutan kinerja peralatan.

Dalam tahap awal penelitian ini, dicoba suatu bentuk sistem peralatan yang memanfaatkan penggunaan komputer IBM PC sebagai sarana pengumpul dan pengolah data. Dalam kaitan ini dicoba beberapa rangkaian dalam bentuk antarmuka yang dipasang pada slot IBM PC, dan dioperasikan dengan kendali IBM PC melalui perangkat lunak yang dirancang. Rangkaian yang dirancang adalah rangkaian anti koinsiden dengan beberapa pencacahnya, sehingga untuk menguji peralatan ini cukup dengan mengambil keluaran dari penguat awal untuk masing masing detektor.

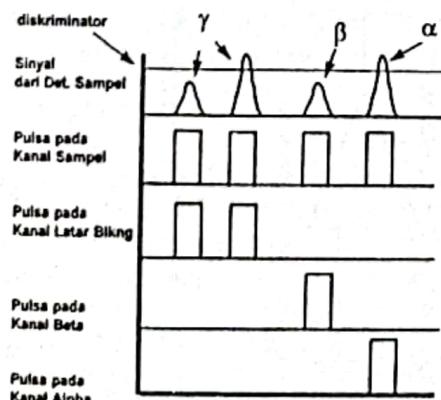

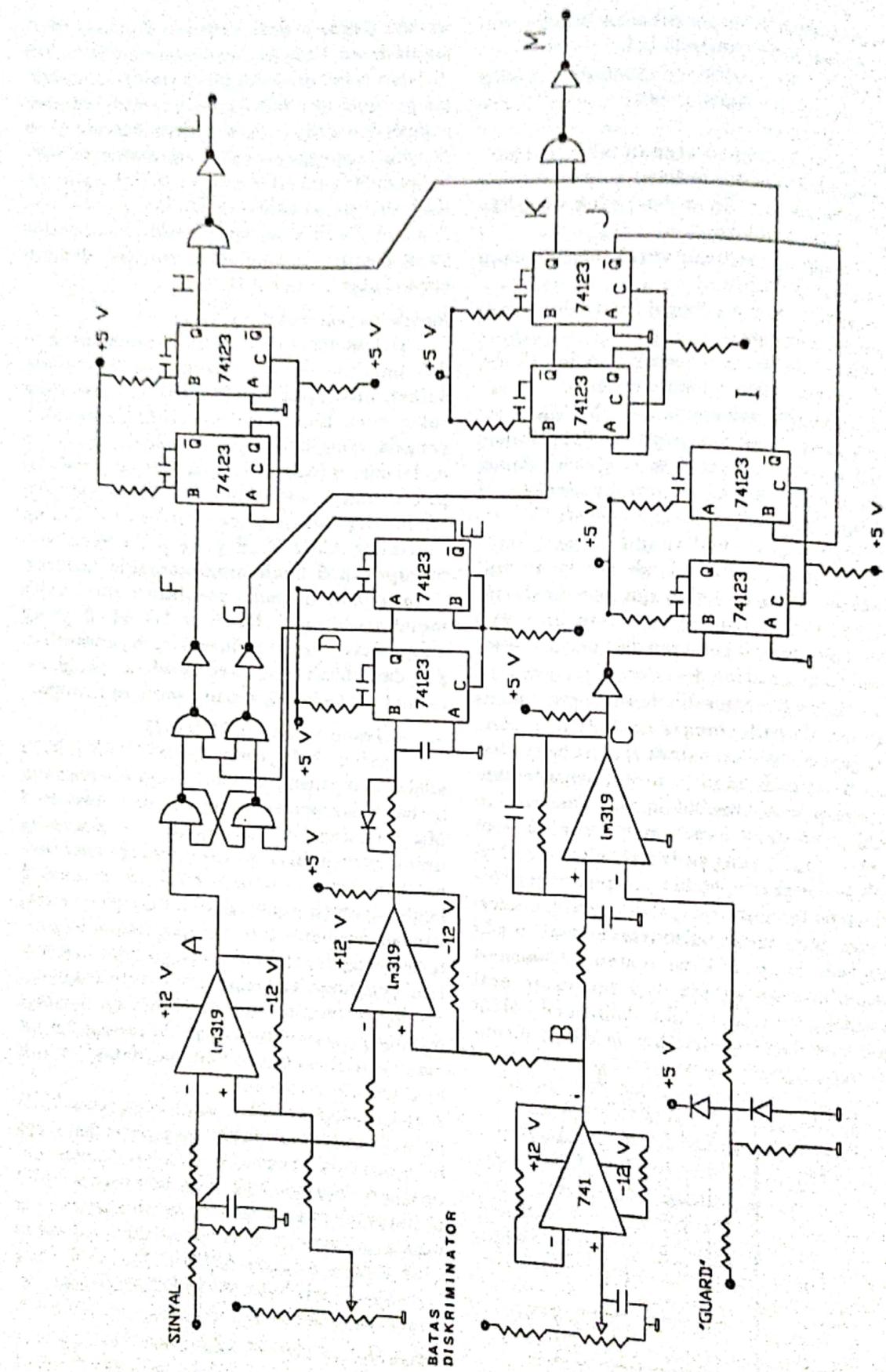

Gambar 3 memperlihatkan diagram pulsa yang terjadi pada rangkaian anti koinsiden. Pada gambar terlihat bahwa apabila hanya terdapat pulsa pada saluran sinyal, maka tergantung tinggi pulsa tersebut, ia akan memberikan sinyal pulsa pada kanal yang sesuai dengan kanal  $\alpha$  atau  $\beta$ , yang pada akhirnya akan tercacak. Sedangkan apabila terjadi pulsa yang bersamaan pada saluran sinyal dan guard, tak tergantung pada tinggi pulsanya, tidak akan ada pulsa keluaran pada kanal  $\alpha$  atau  $\beta$ . Gambar 4 memperlihatkan skema dari rangkaian anti koinsiden. Rangkaian anti koinsiden selain dapat menekan sinyal latar, ia dapat memi-

Gambar 3. Diagram pulsa pada rangkaian anti-koinsiden

sahkan sinyal  $\alpha$  dari sinyal  $\beta$ , dan juga dari sinyal latar. Pada bagian depan rangkaian terdiri dari beberapa buah komparator. Komparator pertama mendapat masukan dari detektor sampel dan sinyal tersebut akan dibandingkan dengan tegangan searah yang diatur sebagai batas antara sinyal  $\alpha$  dan  $\beta$  (ULD). Disamping itu kedua sinyal keluaran detektor sampel dan detektor guard akan masuk pada komparator yang masing masing dibandingkan dengan sinyal batas latar (LLD).

#### Rangkaian pencacahan dan pengala

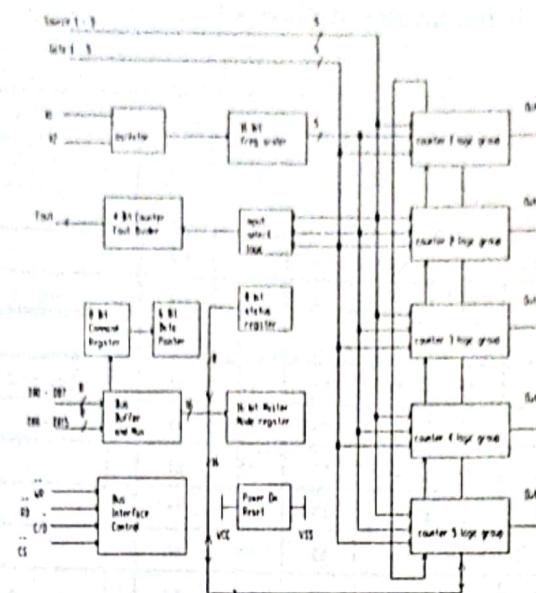

Dalam mencacah radiasi intensitas rendah, untuk memberikan hasil yang dapat dianalisa dibutuhkan waktu pencacahan yang cukup lama. Karena itu dibutuhkan rangkaian pengala yang interval waktunya dapat diatur mulai dari orde detik sampai orde jam, melalui pengaturan perangkat lunak. Dalam kesempatan ini digunakan komponen system timing controller AMD 9513 yang pada dasarnya merupakan 5 buah programmable counter. Secara prinsip pada peralatan ini hanya membutuhkan 1 buah AMD 9513 yang difungsikan sebagai paduan 3 buah pencacah  $\alpha$ ,  $\beta$ ,  $\gamma$  dan 1 buah pengala serta sebuah pengkode alamat untuk kelengkapan pemrogramannya.

#### System Timing Controller AMD 9513

System timing controller (STC) AMD 9513 adalah komponen pendukung bagi sistem yang berbasis mikroprosesor, produk dari Advanced Micro Devices. Rangkaian LSI ini dirancang untuk memenuhi beberapa model aplikasi pencacahan dan pewaktuan. STC ini memuat 5 buah pencacah (counter) 16 bit dengan variasi sumber frekuensi internal dan frekuensi eksternal yang dapat dipilih sebagai masukan melalui pemilihan kontrol program untuk masing-masing pencacah (counter). Selain itu masing-masing pencacah ini dapat dirancang untuk mencacah maju atau mundur dan dalam bentuk bilangan biner atau BCD.

Atas kemampuan inilah maka komponen AMD 9513, dan dapat dirancang sebagai pengala dan beberapa buah pencacah. Gambar 5 memperlihatkan diagram blok dari komponen AMD 9513 penjelasan mengenai prosedur pemrograman komponen tersebut dapat dibaca dengan lebih seksama dalam APPENDIX 5 AM 9513 Data Sheet pada buku Model PCL-830 Counter/Timer Card, User's Manual.

#### Perian register AMD 9513 dan urutan pemograman

Semua data yang ditransfer ke AMD 9513 melalui 2 buah labuhan keluaran/masukan (I/O

Gambar 4. Rangkaian antikoinsiden

Gambar 5. Diagram blok AMD 9513

port). Labuhan dengan alamat dasar + 0 digunakan untuk pengalihan data seperti memuat/membaca cacahan dan counter mode register. Labuhan dengan alamat dasar + 1 digunakan untuk pengalamanan, perintah, kontrol dan tujuan pembacaan status

Karena banyaknya register pada AMD 9513, sistem tak langsung pengaksesan register digunakan melalui internal data pointer register dan kemudian seterusnya dicapai melalui command register.

Bermacam macam kode command register yang legal dituliskan pada Tabel 1. Dalam penggunaan AMD 9513 untuk keperluan peralatan pencacah hanya digunakan perintah perintah dalam grup #1 dan #2 saja. Oleh karena itu dalam kesempatan ini hanya disinggung pelaksanaan perintah dalam grup #1 dan #2 saja.

#### Grup # 1

Semua kode dalam group ini dimulai dengan 000. Kode ini memilih register internal menurut kepada bit E dan G yang membentuk register data pointer. AMD 9513 mempunyai satu master mode register yang mengontrol operasi dari semua counter dan scaler. Register ini harus diatur pada permulaan inisialisasi program. Selain dari pada itu setiap counter mempunyai mode register, load register dan hold register secara tersendiri. Register ini diakses

melalui labuhan dengan alamat dasar +0, setelah membentuk register data pointer pada alamat register yang diinginkan. Format register data pointer terlihat pada Tabel 2. Register data pointer mempunyai sebuah elemen pointer 2 bit (E), sebuah grup pointer 3 bit (G) dan 1 bit byte pointer. Byte pointer menunjukkan apakah lsb atau msb dari suatu data 16 bit yang ditransfer pada tahap selanjutnya. Jika byte pointer (B) diset 1, maka lsb diharapkan untuk ditransfer. Dengan data bus 8 bit pada PC, byte pointer akan berubah mengikuti transfer data 8 bit. Element dan group pointer digunakan untuk memilih internal register yang akan diakses melalui labuhan data (data port).

#### Grup # 2

Grup # 2 membentuk perintah perintah untuk pengaturan counter secara bersama. Semua kode kodenya dimulai dengan 001 sampai 110. Tabel 3 memperlihatkan dari masing masing kode yang dibentuk oleh bit C7, C6, C5. Sedangkan C4 - C0 merupakan kelompok 5 bit (S) pada group ini yang berhubungan dengan masing masing counter. Tiap bit menunjukkan counter yang bersangkutan (S1 = counter 1, S2 = counter 2, S3 = counter 3, dsb). Jika bit S = 1 maka operasi yang tertentu dilaksanakan pada counter yang bersangkutan.

Tabel 1. Susunan kode perintah dengan alamat dasar + 1

| C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |           |

|----|----|----|----|----|----|----|----|-----------|

| 0  | 0  | 0  | 12 | 11 | 04 | 02 | 01 | Group = 1 |

|    |    |    |    |    |    |    |    |           |

| 0  | 0  | 1  | 53 | 54 | 50 | 52 | 51 | Group = 2 |

| 0  | 1  | 0  | 55 | 54 | 53 | 52 | 51 |           |

| 0  | 1  | 1  | 53 | 54 | 53 | 52 | 51 |           |

| 1  | 0  | 0  | 53 | 54 | 53 | 52 | 51 |           |

| 1  | 0  | 1  | 53 | 54 | 53 | 52 | 51 |           |

| 1  | 1  | 0  | 53 | 54 | 53 | 52 | 51 |           |

|    |    |    |    |    |    |    |    |           |

| 1  | 1  | 1  | 0  | 0  | N4 | N2 | N1 | Group = 3 |

| 1  | 1  | 1  | 0  | 1  | N4 | N2 | N1 |           |

| 1  | 1  | 1  | 1  | 0  | N4 | N2 | N1 |           |

|    |    |    |    |    |    |    |    |           |

| 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | Group = 4 |

| 1  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |           |

| 1  | 1  | 1  | 0  | 0  | 1  | 1  | 1  |           |

| 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  |           |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  |           |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  |           |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |           |

#### Master mode register

Master mode register mengatur keseluruhan operasi AMD 9513 dan merupakan register pertama yang diinisialisasi ketika melakukan pemrograman. Register ini merupakan register 16 bit. Dengan register ini kita dapat mengatur apakah komponen tersebut akan diatur untuk dapat mengeluarkan pulsa dengan frekuensi tertentu (fout), mengambil asal sumber frekuensi, besar pembagi frekuensi, pengaturan scaler (binary/BCD division), dan lain-lain. Dalam hal pembuatan pewaktu hal ini sangat berguna untuk mengeluarkan suatu time base

pewaktuan. Keterangan yang lebih lengkap dapat dibaca pada data sheet komponen AMD 9513.

#### Counter mode register

Setiap counter dalam AM 9513 mempunyai masing masing mode register yang mengatur bentuk operasinya. Counter mode register harus di bentuk setelah pembentukan master mode register. Register ini merupakan register 16 bit dan digunakan untuk mengatur pemilihan sumber cacah, pengaturan pencacahan, pengaturan gate dan pengaturan keluaran dari counter.

Tabel 2. Format register data pointer

| Elemen pointer<br>-----<br>E2 E1                                                                                                                        | Counter pointer<br>-----<br>G4 G2 G1 | Byte pointer<br>-----<br>BP                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter group ( E2, E1 ) :<br>0 0 - Mode register<br>0 1 - Load register<br>1 0 - Hold register<br>1 1 - Hold register /<br>hold cycle increment        |                                      | Group pointer ( G4, G2, G1 ) :<br>0 0 0 - illegal<br>0 0 1 - Counter group 1<br>0 1 0 - Counter group 2<br>0 1 1 - Counter group 3<br>1 0 0 - Counter group 4<br>1 0 1 - Counter group 5<br>1 1 0 - Illegal |

| Control group ( E2, E1 ) :<br>0 0 - Alarm register 1<br>0 1 - Alarm register 2<br>1 0 - Master mode register<br>1 1 - Status register /<br>no increment | +                                    | 1 1 1 - always for control<br>group                                                                                                                                                                         |

| Byte pointer ( BP )<br>0 - Most significant byte transferred next<br>1 - Least significant byte transferred next                                        |                                      | Note : This bit cannot be controlled through command code but<br>can be read through status register. This bit is set to 1<br>when the data pointer register is loaded.                                     |

Tabel 3. Kode perintah untuk grup # 2

| C7 | C6 | C5 | Description                                |

|----|----|----|--------------------------------------------|

| 0  | 0  | 1  | - Arm counting for selected counters (S=1) |

| 0  | 1  | 0  | - Load source into specified counters      |

| 0  | 1  | 1  | - Load and arm specified counters          |

| 1  | 0  | 0  | - Disarm and save all selected counters    |

| 1  | 0  | 1  | - Save selected counters in hold registers |

| 1  | 1  | 0  | - Disarm all selected counter              |

### Perangkat lunak & algoritma pemrograman AMD9513

Pengoperasian peralatan ini sangat tergantung pada perangkat lunaknya. Dalam hal ini perangkat lunak dibuat dengan menggunakan bahasa Microsoft Quick Basic. Pada garis besarnya perangkat lunak ini mengatur kerja dari pencacah PCL 830 dengan komponen inti AMD 9513 membentuk 3 buah pencacah yang masing-masing untuk kanal  $\alpha$ ,  $\beta$  dan  $\gamma$  dengan selang waktu pencacahan yang variabel dengan menampilkan hasil cacahan secara kontinyu untuk selama selang waktu yang dilaluinya pada layar monitor.

Untuk mengoperasikan AMD 9513 sesuai sistem yang diinginkan, maka disusun program untuk mengoperasikan AMD 9513.

1. Bentuk master mode register untuk mengatur pembagian sumber frekwensi.

2. Bentuk counter mode untuk counter 0 sebagai pembagi untuk mengeluarkan sinyal time base 1 Hz.

3. Bentuk counter mode untuk counter 1 sebagai penghitung waktu pencacahan

4. Bentuk counter mode untuk counter 2 sebagai pencacah untuk radiasi  $\alpha$ .

5. Bentuk counter mode untuk counter 3 sebagai pencacah untuk radiasi  $\beta$ .

6. Bentuk counter mode untuk counter 4 sebagai pencacah untuk radiasi  $\gamma$ .

7. Jalankan semua counter, dan baca semua isi counter, simpan di hold register dan tampilkan nilai cacahan.

8. Hentikan pencacahan manakala isi counter 1 telah mencapai waktu pencacahan yang diinginkan.

### HASILDAN PEMBAHASAN

Pengujian pendahuluan dilakukan di laboratorium dengan menguji rangkaian pencacah secara tersendiri menggunakan generator pulsa standar, demikian juga pengujian rangkaian anti koinsiden. Setelah uji laboratorium memberikan hasil yang baik barulah dilakukan uji pengukuran dari peralatan ini dengan cara mengukur sinyal dari suatu sistem deteksi yang sudah ada dari peralatan Canberra dengan sumber radiasi standar dan ternyata dapat menunjukkan bahwa sistem rangkaian anti koinsiden dan pencacah dapat berfungsi dengan baik. Berikut adalah hasil uji pengukuran dengan menggunakan beberapa bahan standar yang dilukiskan pada Tabel 4.

Dari hasil pengukuran dapat disimpulkan bahwa rangkaian yang diuji untuk sistem tersebut bersfungsi dengan baik. Terlihat pada percobaan 1 dan 2 dengan membandingkan cacahan pada berkas latar1.dat dan latar2.dat adanya efektivitas rangkaian anti koinsiden untuk menekan latar. Pada percobaan 3 dan 4 dengan melihat data cacahan pada berkas AM241.dat dan SR90.dat terlihat adanya efektivitas untuk memisahkan  $\alpha$  dan  $\beta$  sedangkan analisa lebih lanjut dalam pengukuran dapat dikembangkan perangkat lunak yang lebih baik dan rancangan perangkat keras tambahan.

### KESIMPULAN DAN SARAN

Pada dasarnya keseluruhan sistem pencacah  $\alpha$  dan  $\beta$  dengan penekanan latar belakang bersfungsi dengan baik dan dapat dibuat secara lebih lengkap dalam suatu rangkaian antarmuka pada IBM PC. Misalnya untuk mendapatkan harga optimum dari tegangan tinggi dapat dibuatkan suatu variabel tegangan tinggi

Tabel 4. Hasil pengukuran

| No. | Nama berkas         | Tegangan tinggi | Diskriminator | Lama pencacahan | Cacahan $\alpha$ | Cacahan $\beta$ | Keterangan                             |

|-----|---------------------|-----------------|---------------|-----------------|------------------|-----------------|----------------------------------------|

| 1.  | Latar 1. dat Jan 94 | 1000 V          | 3 volt        | 1 jam           | 0                | 5               | Pencacahan latar dengan anti koinsiden |

| 2.  | Latar 2. dat Jan 94 | 1000 V          | 3 volt        | 1 jam           | 0                | 11              | Pencacahan latar tanpa anti koinsiden  |

| 3.  | AM241. dat Jan 94   | 1430 V          | 3 volt        | 2 mnt           | 9842             | 1049            | AM241 sebagai sumber $\alpha$          |

| 4.  | SR90. dat Jan 94    | 1430 V          | 3 volt        | 2 mnt           | 80               | 48510           | SR90 sebagai sumber $\beta$            |

yang dikontrol IBM PC sehingga dapat dicari daerah *plateau* dari detektor setiap diperlukan, demikian juga dengan penentuan diskriminasi yang merupakan tegangan searah sebagai batas antara tinggi pulsa sinyal  $\alpha$  dan  $\beta$  yang harus ditentukan lebih teliti dapat dibuatkan melalui

suatu perangkat keras tambahan seperti pengubah digital ke analog. Penambahan rangkaian rangkaian tersebut di atas dan pengembangan perangkat lunaknya untuk proses data pengukuran selanjutnya sedang dalam tahap penyelesaian.

## DAFTAR PUSTAKA

1. Anonim, User's Manual, Model PCL-830 Counter/Timer Card Advantech Co. Ltd Taiwan, (1993).

2. Anonim, Experiments in Nuclear Science, Ortec (1976).

3. Anonim, Alpha/Beta System Model 2400, Operator's manual Canberra.

4. Nicholson, P.W., Nuclear Electronics John Willey & Sons, London (1987).